PRODUCT

AN/ZY-9461-SDR

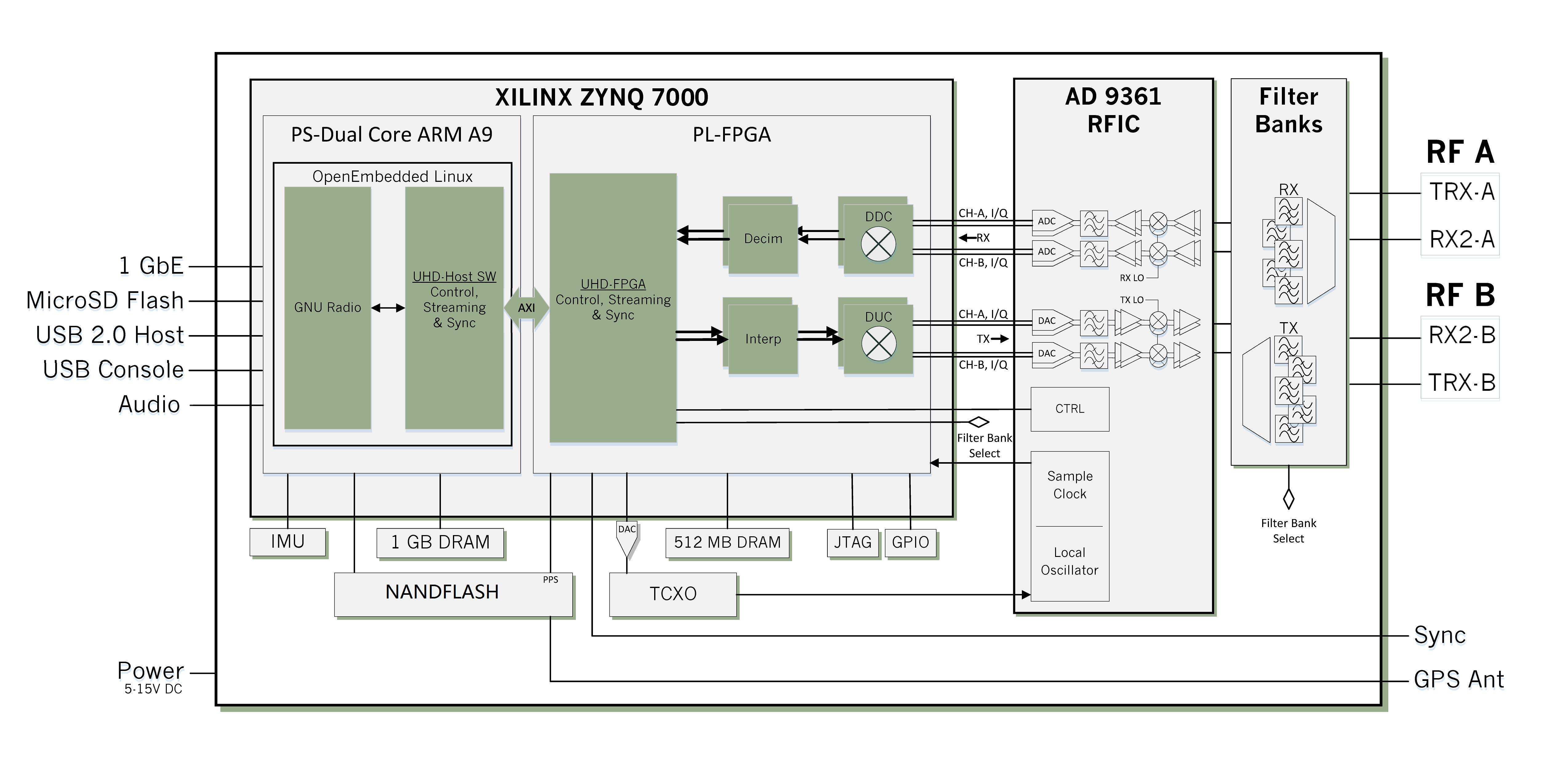

AN/ZY-9461-SDR数据平台综合板是一个可以独立运行的软件无线电平台。射频前端采用AD9361收发器,并且可以支持2*2 MIMO。基带处理器采用的是xilinx的zynq7045 FPGA芯片,改FPGA芯片内嵌ARM双核CPU。并集成了USB、网口、SPI、UART等丰富的外设,适用该平台,用户可以快速的进行原型设计和开发嵌入式应用程序。

板卡主要功能包括:

l 为基带和中频信号处理提供可重配置的硬件平台

l 为信号处理算法提供丰富的 FPGA 资源

l 提供到中频及射频的数据、控制接口

l 提供扣卡接插件,用于实现特定功能

l 上电及复位后所有接口代码复位

l 提供简单易用的平台管理接口

3.1硬件架构

AN/ZY-9461-SDR高性能基带信号处理板卡采用Xilinx公司Zynq7000系列FPGA芯片和AD9361射频芯片进行设计。板卡采用80*60紧凑型尺寸结构。

3.2详细指标

|

指标名词 |

具体指标 |

|

板卡尺寸 |

80*60mm |

|

处理能力 |

支持选配Zynq7030/35/45, 提供丰富的FPGA编程资源 提供双核ARM A9 CPU,运行主频高达800MHz |

|

对外接口 |

1个10M/100M/1000M网口 1个USB2.0接口 1个FMC 80pin连接器接口 |

|

板卡存储容量 |

1GB DRAM 8G NAND FLASH |

|

程序加载方式 |

JTAG加载 SD卡加载 NANDFLASH加载 |

|

工作频段 |

70~6000MHz,步进调整2.4Hz |

|

收发通道数 |

2发2收 |

|

信号带宽 |

200KHz~56MHz,软件可配置 |

|

跳频速率 |

>=2000hop/s |

|

最大输出功率 |

10dBm |

|

本振泄露 |

-50dBc |

|

镜像抑制 |

-50dBc |

|

发射动态范围 |

80dB,调整步进0.25dB |

|

接收动态范围 |

76dB,调整步进1dB |

|

外部参考时钟 |

可选 |

|

工作模式 |

TDD/FDD,软件可配置 |

|

采样速率 |

ADDA 12bit/250Msps,采用速率用户可配置 |

|

数字资源 |

自带128阶FIR滤波器,用户可配置 |

|

变速率资源 |

自带抽取、插值滤波器,可配置为2/4/8倍 |